Clear Sky Science · de

Thermisches Management heterogen integrierter 3‑D‑Mikroelektronik: Herausforderungen und künftige Forschungsrichtungen

Warum das Stapeln von Chips Ihre Alltagsgeräte verändert

Von Smartphones und Laptops bis zu Rechenzentren für künstliche Intelligenz: Unsere Elektronik wird immer kompakter und gleichzeitig leistungsfähiger. Um das zu erreichen, stapeln Ingenieure heute verschiedene Chiparten übereinander und schaffen so kompakte dreidimensionale Gehäuse. Dieser clevere Schritt erhöht die Leistung und reduziert Signalverzögerungen, hat aber den Nachteil, dass sehr viel Wärme auf kleinem Raum eingeschlossen wird. Der übersichtsartige Artikel erklärt, warum Wärme zu einer der größten Gefahren für diese neue Elektronikgeneration geworden ist — und was Forschende tun, damit diese winzigen Silizium‑Hochhäuser nicht überhitzen.

Kleine Hochhäuser der Elektronik bauen

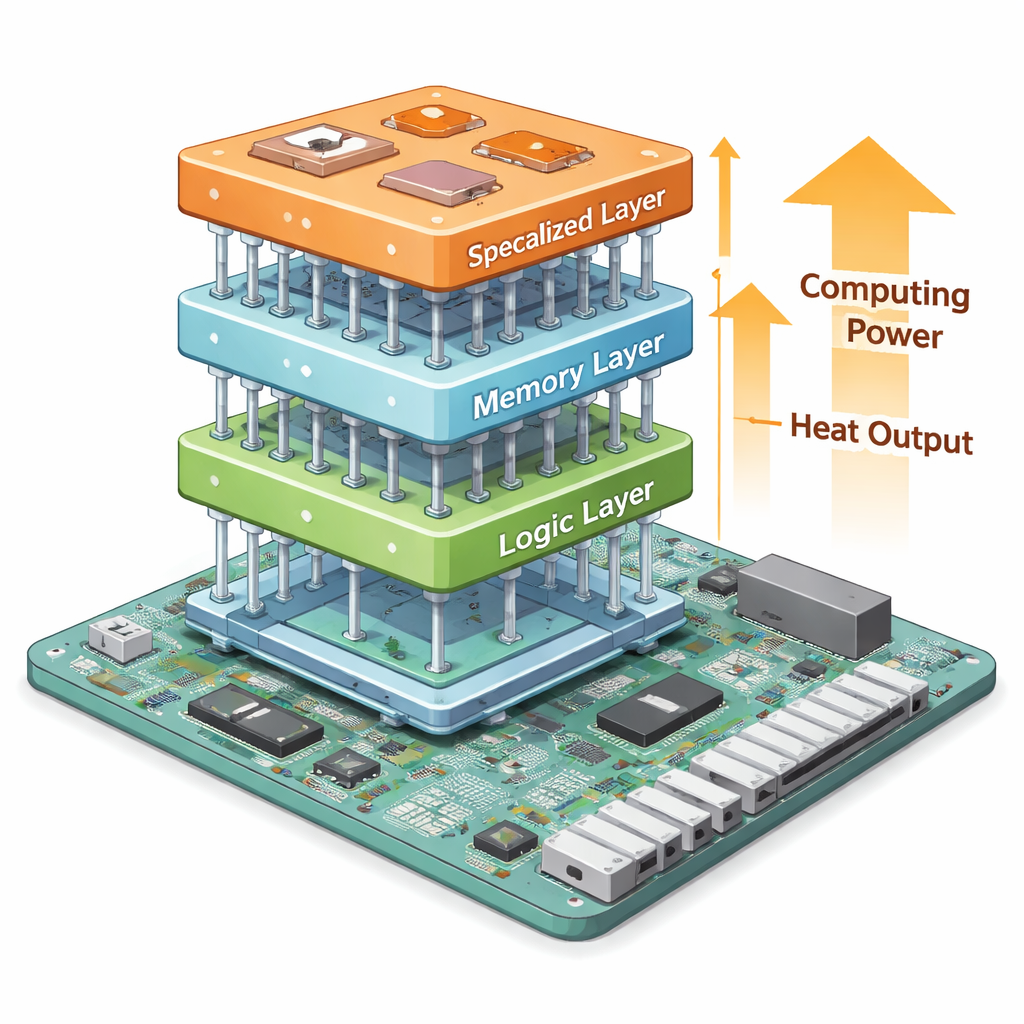

Traditionelle Chips sind meist flach: Schaltungen liegen nebeneinander auf einer einzigen Siliziumscheibe. Da das weitere Schrumpfen von Strukturen in zwei Dimensionen schwieriger wird, setzt die Industrie auf dreidimensionale heterogene Integration, bei der mehrere Lagen verschiedener Chips — Logik, Speicher, Funk, Photonik und mehr — vertikal gestapelt und durch Metallpfeiler verbunden werden. Diese Anordnung verkürzt Kommunikationswege und erlaubt es Designern, Technologien aus unterschiedlichen Fertigungen zu kombinieren. Das Ergebnis sind schnellere Verarbeitung, geringere Verzögerungen und effizienterer Energieeinsatz, was besonders für künstliche Intelligenz, Cloud‑Computing und fortschrittliche Kommunikationssysteme wertvoll ist.

Der versteckte Preis für mehr Leistung auf engem Raum

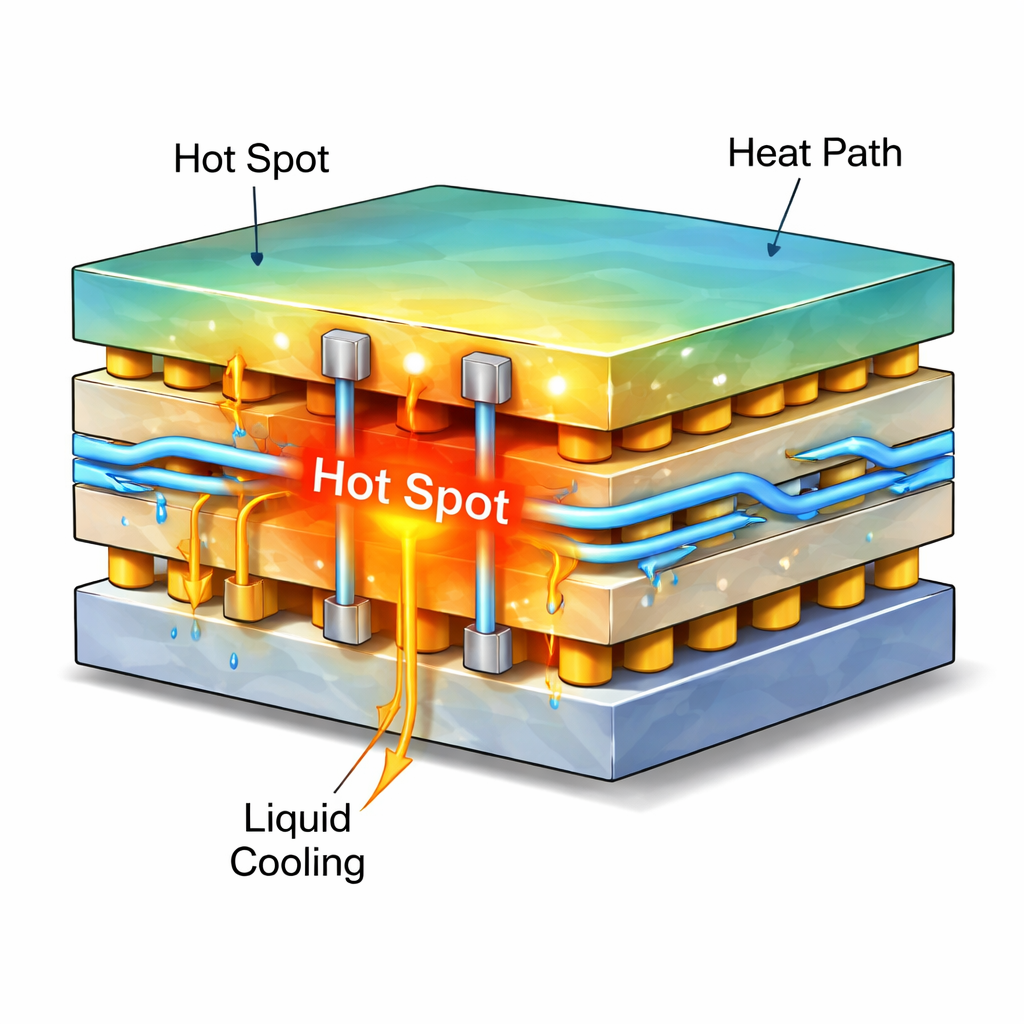

So dichtes Stapeln hat einen ernsten Nachteil: Wärme findet schlechter einen Ausweg. Jede Schicht erzeugt Wärme durch bekannte elektrische Verluste — Widerstände in Leitungen, Schalter, die ein‑ und ausschalten, und kleine Leckströme, die nie ganz verschwinden. In 3‑D‑Stapel addieren sich diese Verluste, und die mittleren Lagen, am weitesten von den Kühlflächen entfernt, werden am heißesten. Die Temperatur kann ungleichmäßig ansteigen und Hotspots bilden, die nur einen Bruchteil eines Millimeters groß, dafür aber deutlich heißer als ihre Umgebung sind. Schon wenige Grad über dem vorgesehenen Betriebsbereich können die Zuverlässigkeit stark verringern, den Verschleiß beschleunigen und in Extremfällen eine sich selbst verstärkende Spirale aus steigender Temperatur und steigendem Strom — bekannt als thermisches Durchgehen — auslösen.

Wenn Wärme sich ausbreitet, verformt und Schaden anrichtet

Die Übersichtsarbeit macht deutlich, dass Temperaturprobleme nicht nur ein warm laufender Chip sind; sie können das gesamte Paket still und heimlich beschädigen. Unterschiedliche Materialien im Stapel — Silizium, Metalle, Polymere und Keramiken — dehnen sich beim Erwärmen unterschiedlich stark aus. Wenn das Bauteil zwischen Leerlauf und Volllast wechselt, entstehen mechanische Spannungen, die Lötverbindungen zum Riss bringen, Zwischenflächen öffnen und die metallgefüllten vertikalen Verbindungen beschädigen können. Gleichzeitig führt ungleichmäßige Erwärmung zu thermischem Crosstalk: Ein heißer Logik‑Die kann unbeabsichtigt eine stromsparende Speicher‑ oder Optiklage darüber erwärmen und deren Leistung verschlechtern. Im Lauf der Zeit wachsen kleine Hohlräume und Risse rund um wärmeleitende Strukturen, erhöhen den thermischen Widerstand und erschweren das Abführen der Wärme genau dort, wo es am wichtigsten ist.

Neue Methoden, Wärme dreidimensional zu transportieren

Um diese Probleme zu bewältigen, überdenken Forschende jeden Abschnitt des thermischen Pfads. Manche Strategien zielen darauf ab, Wärme innerhalb des Stapels besser zu verteilen, etwa durch verbesserte Unterfüllungen und Zwischenlagermaterialien, die Wärme gut leiten, ohne elektrische Signale zu stören. Andere nutzen die vertikalen Metallpfeiler als dedizierte Wärmeleiter oder fügen zusätzliche, nur für Wärme gedachte Pfeiler neben den Signalwegen hinzu. Der Artikel hebt auch einen Trend hervor, das Kühlsystem deutlich näher an die Wärmequelle zu bringen. Winzige Flüssigkeitskanäle und Wälder mikroskopischer Pin‑Fins können direkt in oder zwischen den Chip‑Schichten geätzt werden, sodass Kühlmittel nur wenige zehn Mikrometer von den heißesten Stellen entfernt fließen. Diese eingebetteten Kühler können extreme Wärmestromdichten abführen und den Durchfluss an die Bedürfnisse jeder Schicht anpassen, bringen jedoch neue Probleme in Bezug auf mechanische Festigkeit, Fertigungskomplexität und Langzeitzuverlässigkeit bei Druck und Feuchtigkeit mit sich.

Wohin sich das Feld als Nächstes entwickelt

Insgesamt kommt der Artikel zu dem Schluss, dass die Beherrschung von Wärme weitgehend bestimmen wird, wie weit 3‑D‑gestapelte Elektronik vorankommen kann. Keine einzelne Lösung reicht aus: Chiplayout, Materialien, vertikale Verbindungen, Grenzflächen und Kühlkanäle müssen gemeinsam entworfen werden, statt isoliert betrachtet zu werden. Zukünftige Arbeit wird sich auf skalierbare Wege konzentrieren, hochleitfähige, mechanisch kompatible Materialien mit herstellbaren, niedertemperaturigen Prozessen zu verbinden, sowie auf intelligentere Entwurfswerkzeuge, die das thermische Verhalten gleichberechtigt mit Geschwindigkeit und Leistung behandeln. Können diese Hürden überwunden werden, könnten dreidimensionale Chipstapel weiterhin mehr Rechenleistung in immer kleineren Gehäusen liefern — ohne sich selbst zu überhitzen.

Zitation: Sharma, M.K., Ramos-Alvarado, B. Thermal management of 3-D heterogeneously integrated microelectronics: challenges and future research directions. Commun Eng 5, 28 (2026). https://doi.org/10.1038/s44172-026-00590-y

Schlüsselwörter: 3D‑Chip‑Stapelung, Elektronikkühlung, thermisches Management, mikrofluidische Kühlung, heterogene Integration