Clear Sky Science · de

Kartierung vielfältiger Hysterese‑Dynamiken in skalierten MoS2-FETs mittels einer universellen Methode aus TCAD‑Modellierung

Warum winzige Schalter verlässliches Verhalten brauchen

Die moderne Elektronik strebt auf immer kleinere Transistoren zu, und zweidimensionale (2D) Materialien wie Molybdändisulfid (MoS2) zählen zu den vielversprechenden Kandidaten für künftige Chips. Mit der Verkleinerung der Schalter wird ihr Verhalten jedoch oft inkonsistent: Dasselbe Bauteil kann je nach unmittelbarer Vorbenutzung unterschiedlich reagieren. Dieser speicherähnliche Effekt, Hysterese genannt, wird häufig als kleines Ärgernis abgetan. In dieser Arbeit zeigen die Autoren, dass die Hysterese tatsächlich eine Fülle von Informationen über verborgene Fehler in fortschrittlichen Transistoren verbirgt — und sie stellen eine universelle Methode vor, um diese Informationen auszulesen.

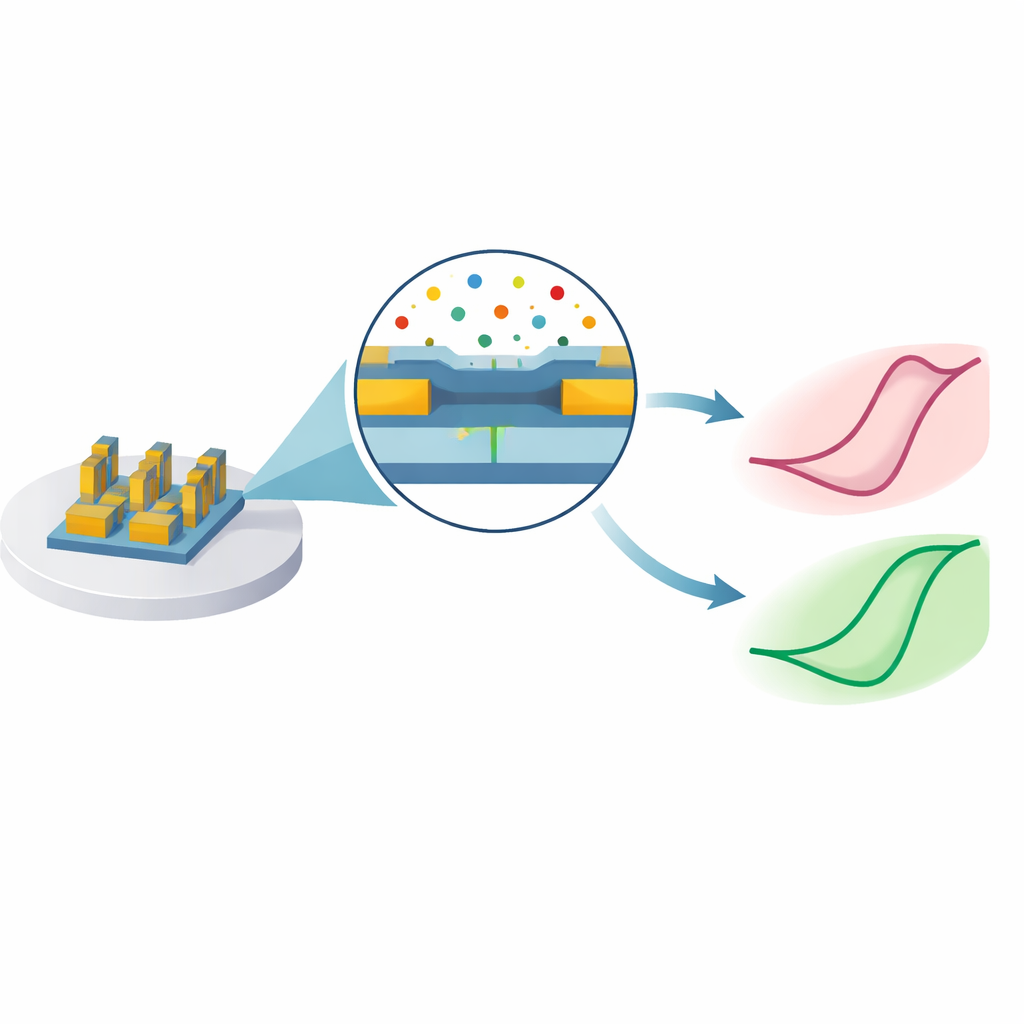

Wie Transistoren der nächsten Generation aufgebaut sind

Zukünftige 2D‑Feldeffekttransistoren verwenden eine ultradünne MoS2‑Schicht als Kanal, in dem der Strom fließt, darüber eine sehr dünne isolierende Oxidschicht wie Hafniumoxid (HfO2) und obenauf ein Metallgate. Um Bauteile weiter zu verkleinern, muss dieses Oxid elektrisch betrachtet quasi nur ein Nanometer dick sein, sodass bereits einzelne Defekte darin den Kanal stark stören können. Diese Defekte wirken als winzige Fallen, die zeitweise elektrische Ladung binden oder freisetzen können. Weil sich Defekte in verschiedenen Tiefen des Oxids befinden und sowohl mit dem Kanal als auch mit dem Gate wechselwirken können, kann ihr kollektives Verhalten den Transistor auf subtile Weise stabilisieren oder destabilisieren. Dieses Defekt‑Profil zu verstehen, ist entscheidend, damit 2D‑Transistoren mit heutiger Siliziumtechnologie konkurrieren können.

Warum der Transistor sich an seine Vergangenheit erinnert

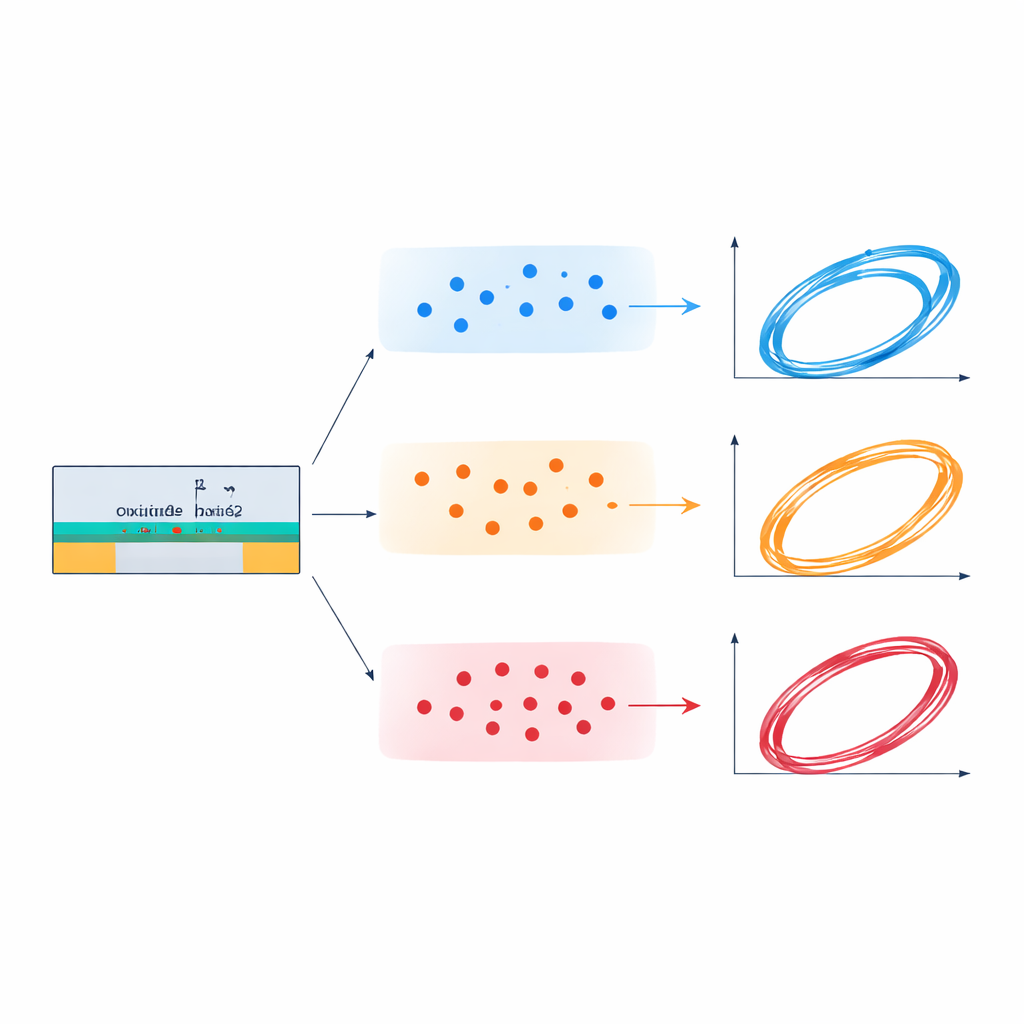

Wenn Ingenieure die Gate‑Spannung auf‑ und abfahren und den Strom aufzeichnen, stellen sie oft fest, dass Vorwärts‑ und Rückwärtsfahrt nicht zusammenfallen. Diese Schleife ist die Hysterese. Üblicherweise messen Forscher den Abstand zwischen den beiden Kurven an einem einzigen Betriebspunkt und bezeichnen diesen als Hysteresebreite, oft mit dem Schluss, sie sei „klein“ oder „vernachlässigbar“. Die Autoren argumentieren, dass diese Praxis irreführend ist, besonders bei skalierten Bauteilen, in denen verschiedene Defektgruppen entgegengesetzte Beiträge leisten können. Abhängig von Messgeschwindigkeit und Betriebsstrom kann derselbe Transistor konventionelle im Uhrzeigersinn verlaufende Schleifen, umgekehrte gegen den Uhrzeigersinn laufende Schleifen, Umschaltungen zwischen beiden oder sogar nahezu keine Hysterese zeigen, wenn sich gegensätzliche Effekte aufheben.

Eine universelle Karte, verborgen in den Kurven

Um diese Komplexität zu entwirren, nutzt das Team detaillierte Computersimulationen (TCAD) nanoskaliger MoS2‑Transistoren mit gezielt kontrollierten Defektpopulationen in unterschiedlichen Tiefen des Oxids. Anschließend schlagen sie eine universelle Methode zur Hysterese‑Kartierung vor. Statt einer einzelnen Zahl scannen sie die Hysteresebreite über einen großen Strombereich — von knapp über dem Ausschaltzustand bis nahe am Einschaltzustand — und für Messzeiten, die viele Größenordnungen abdecken. Das erzeugt Tausende von Kurven, die zeigen, wie sich die Hysterese bei verschiedenem Mess‑Tempo für jeden Strom ändert. Daraus definieren sie obere und untere „universelle Hysteresefunktionen“, die alle möglichen Verhaltensweisen einschließen. Diese Hüllen zeigen eindeutig, welche Arten von Defekten aktiv sind, ob sie hauptsächlich mit dem Kanal oder mit dem Top‑Gate interagieren und ob sie im Uhrzeigersinn oder gegen den Uhrzeigersinn wirkende Schleifen begünstigen.

Verknüpfung schneller Schleifen mit langfristigem Drift

Die gleichen Defekte, die Hysterese verursachen, treiben auch langsame Drifts im Transistorverhalten unter längerer Beanspruchung an — ein Problem, das als Bias Temperature Instability (BTI) bekannt ist. Durch die Simulation standardisierter Stress‑und‑Erholungs‑Experimente verbinden die Autoren Merkmale in ihren Hysterese‑Karten mit ungewöhnlichen BTI‑Signaturen, etwa einer scheinbaren negativen Verschiebung, die sich später wieder zu einer positiven hin entspannt. Sie zeigen, dass Fallen nahe am Kanal zu langsamen, weitgehend permanenten Verschiebungen neigen, während Fallen näher am Gate schnellere, aber überwiegend reversible Änderungen verursachen. Ihre Methode lässt sich nicht nur auf simulierte MoS2‑Bauteile anwenden, sondern auch auf Messdaten realer MoS2‑ und WSe2‑Transistoren aus Forschungsreinstlabors und Pilotfertigungslinien, einschließlich Fällen, in denen driftende Ionen im Oxid am Ladungstrapping beteiligt sind.

Von komplexen Daten zu praktischer Orientierung

Indem unübersichtliche Hystereseschleifen in standardisierte Karten überführt werden, bietet diese Arbeit ein leistungsfähiges Diagnosewerkzeug für aufkommende Transistortechnologien. Die Methode funktioniert direkt auf experimentellen Datensätzen und erfordert keinen Zugriff auf aufwendige Simulationstools, wodurch sie in vielen Laboren breit einsetzbar ist. Für Ingenieure lautet die zentrale Botschaft: Hysterese ist nicht nur ein zu minimierender Makel, sondern ein Fingerabdruck zugrunde liegender Zuverlässigkeitsprobleme. Das Entschlüsseln dieses Fingerabdrucks mit der vorgeschlagenen Kartierungsmethode kann zu besseren Materialien, saubereren Grenzflächen und klügeren Prozessen führen und so helfen, 2D‑Transistoren von vielversprechenden Prototypen zu verlässlichen Bausteinen künftiger Elektronik zu machen.

Zitation: Lv, Y.Z., Wu, Y.H., Cai, H.H. et al. Mapping diverse hysteresis dynamics in scaled MoS2 FETs using the universal method derived from TCAD modeling. npj 2D Mater Appl 10, 35 (2026). https://doi.org/10.1038/s41699-026-00671-8

Schlüsselwörter: 2D‑Transistoren, Hysterese, Oxiddefekte, Bauteilzuverlässigkeit, MoS2‑FETs