Clear Sky Science · de

3D LineExplore: eine 3D-Leitungs-Explorationsmethode für geometrisches Routing auf mehrlagigen Leiterplatten

Intelligenteres Verdrahten der Platinen in allen Geräten

Jedes Smartphone, jeder Laptop und jedes Auto verbirgt heute winzige Kupferautobahnen, die Signale zwischen Chips transportieren. Während die Elektronik immer mehr Bauteile auf immer weniger Raum zusammenpresst, ist das Zeichnen dieser mikroskopischen „Straßen“ auf Leiterplatten (PCBs) zu einem der schwierigsten Schritte im Hardware-Design geworden. Dieses Papier stellt eine neue Methode zur automatischen Planung dieser Routen in drei Dimensionen vor, die schnellere Entwürfe, weniger Fehler und bessere Leistung für die Geräte verspricht, die wir täglich benutzen.

Warum traditionelles Routing an Grenzen stößt

Die heutigen automatischen PCB-Router denken meist in Form eines schachbrettartigen Rasters: Die Platine wird in winzige Quadrate unterteilt, und Algorithmen wie A* suchen den günstigsten Weg von einem Pin zum anderen. Das funktioniert, bringt aber Kompromisse mit sich. Ist das Raster grob, sind Wege ungenau und können Designregeln verletzen. Ist das Raster sehr fein, explodiert die Suchgröße und wird quälend langsam, besonders bei mehrlagigen Platinen, auf denen Leiterbahnen über kleine gebohrte Löcher, sogenannte Vias, zwischen Lagen springen können. Gitterlose Methoden vermeiden das künstliche Raster und arbeiten direkt mit Formen, waren bisher aber überwiegend auf flache, zweidimensionale Layouts beschränkt und tun sich schwer damit, echtes 3D-Mehrlagen-Routing effizient zu handhaben.

Ein 3D-„Radar“ zur Suche sicherer Wege

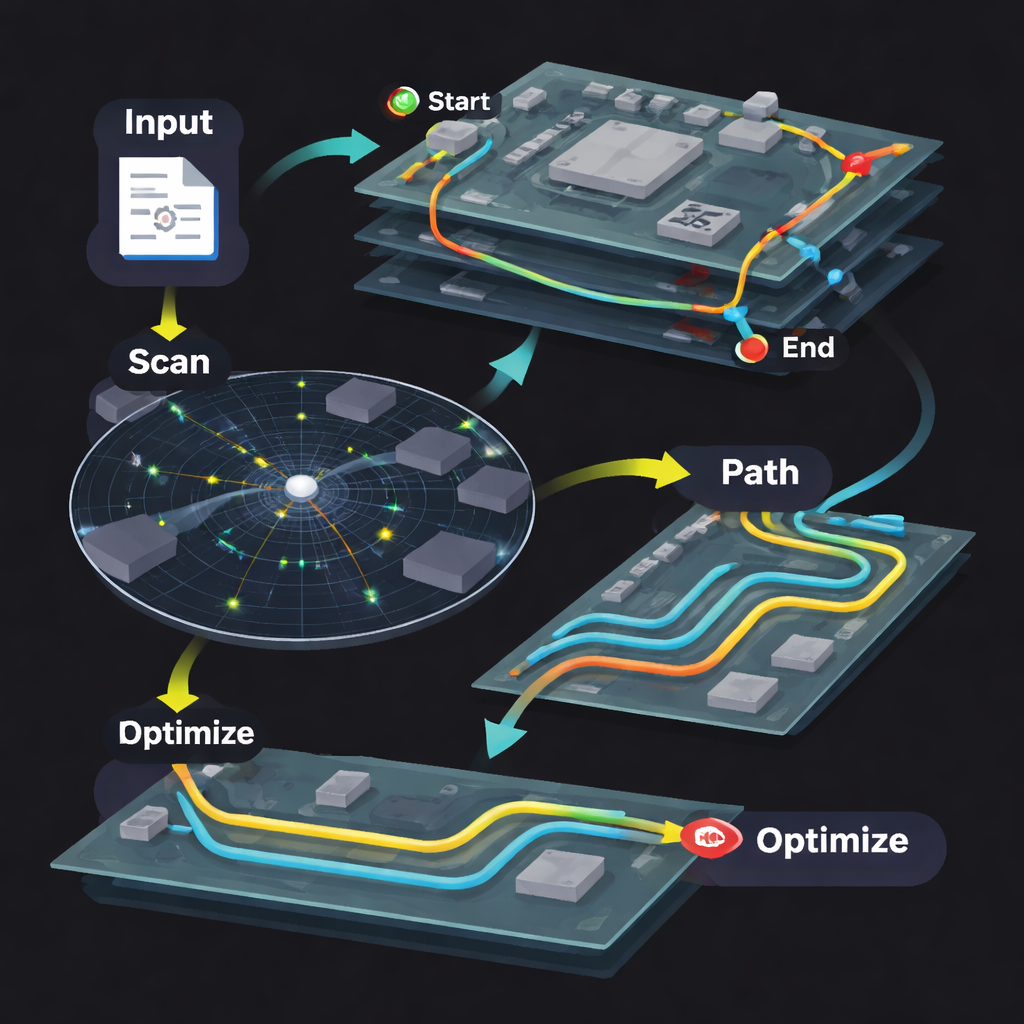

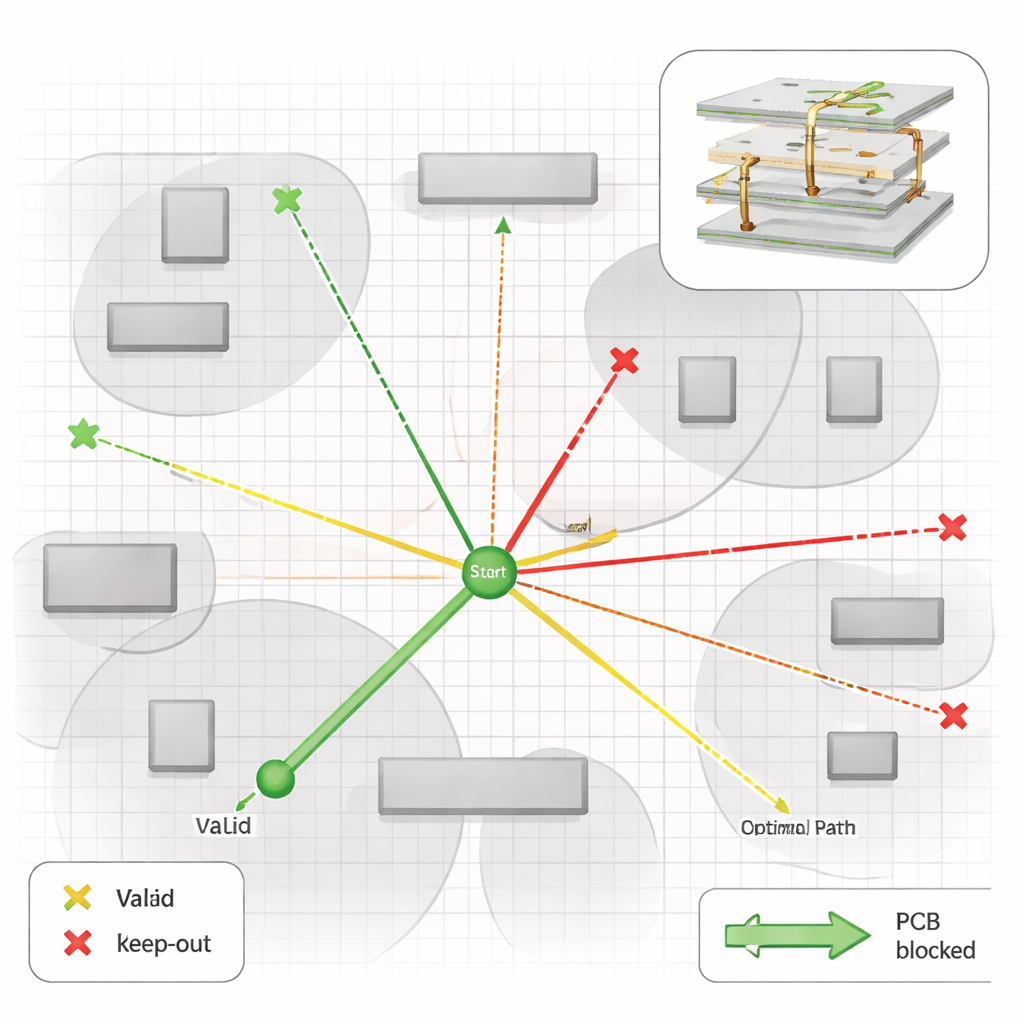

Die Autoren stellen 3D LineExplore vor, eine gitterlose Routing-Methode, die direkt im kontinuierlichen Raum über mehrere Lagen arbeitet. Im Kern steht ein am Radar inspiriertes Scanverfahren. Anstatt jedes Rasterfeld zu prüfen, betrachtet die Methode die Umgebung des aktuellen Punktes lokal, identifiziert nahe Hindernisse wie Bauteile und bereits platzierte Leiterbahnen und sammelt markante Eckpunkte dieser Formen. Daraus schlägt sie eine kompakte Menge vielversprechender „Explorationspunkte“ vor, durch die eine Leitung sicher führen könnte. Liefert die unmittelbare Nachbarschaft keinen Pfad, vergrößert sich der Scanradius, aber nur wenn nötig. Dieses selektive Abtasten hält die Suche fokussiert, vermeidet redundante Prüfungen und lässt sich auf natürliche Weise auf mehrere Lagen erweitern, indem Zielpunkte zwischen Lagen projiziert und spezielle Explorationspunkte hinzugefügt werden, die potenzielle Via-Standorte repräsentieren.

Die Kosten den besten Weg bestimmen lassen

Sind die Explorationspunkte bekannt, wählt ein zweites Modul den eigentlichen Pfad. Dieser heuristische Pfadalgorithmus zur Hindernisvermeidung arbeitet wie eine geführte Suche: Er gewichtet die bereits zurückgelegte Distanz, die Entfernung zu jedem nächsten Kandidatenpunkt, die Zusatzkosten für das Bohren eines Vias zu einer anderen Lage und eine geradlinige Schätzung der verbleibenden Entfernung zum Ziel. Durch die Kombination dieser Faktoren in einer einzigen Kostenfunktion und einer Prioritätswarteschlange erweitert der Algorithmus immer den vielversprechendsten nächsten Schritt. Im Hintergrund entsteht so ein dünn geknüpftes Graphnetz möglicher Bewegungen, ohne jemals ein vollständiges Gitter zu legen. Wird der Zielpin erreicht, wird der Pfad rekonstruiert, indem gespeicherte Vorgänger-Links zurück zum Start verfolgt werden, was eine vollständige 3D-Route ergibt, die um Hindernisse herumführt und Lagen nur dann wechselt, wenn die zusätzlichen Kosten dies rechtfertigen.

Komplexe Netze bereinigen und Leitungen glätten

Auf realen Platinen wird selten nur ein Pin-Paar gleichzeitig verbunden. Viele Netze verbinden drei oder mehr Pins, was leicht zu Sackgassen oder verhedderten Routen führen kann. 3D LineExplore geht diese Fälle an, indem ein Mehr-Pin-Netz in eine Folge von nächstgelegenen Pin-Paaren zerlegt, diese nacheinander geroutet und anschlie�end fehlende Verbindungen repariert werden. Kann eine Verbindung nicht wie geplant hergestellt werden, sucht der Algorithmus nach einer alternativen Anbindung an einen nahegelegenen bereits verbundenen Pin und stellt das Netz mit minimal zusätzlicher Leitung wieder her. Nachdem alle Verbindungen gesichert sind, verbessert eine Nachbearbeitungsstufe die physische Form der Leiterbahnen. Viele Hochgeschwindigkeits-Designs bevorzugen Biegungen von etwa 135 Grad statt scharfer rechter Winkel, um die Fertigung zu erleichtern und elektrische Reflexionen zu reduzieren. Die Autoren führen eine geometrische „Parallelogramm“-Anpassung ein, die Polyliniensegmente in glattere, auf 135 Grad beschränkte Pfade umformt, dabei alle Verbindungen erhält und neue Kollisionen vermeidet.

Die neue Methode im Test

Das Team bewertete 3D LineExplore an elf öffentlichen Benchmark-Platinen von einfach bis komplex und verglich es mit kommerziellen und akademischen Werkzeugen, darunter FreeRouting, ELECTRA, DeepPCB und einem optimierten 3D-A*-Algorithmus. In diesen Fällen verband die neue Methode etwa 98 % der erforderlichen Pin-Paare erfolgreich und erreichte damit das Niveau etablierter Router oder übertraf es. Auffälliger war, dass die Gesamtlänge der Leitungen im Mittel kürzer war – etwa 15 % weniger als bei einem führenden kommerziellen Werkzeug – was hilft, Signallaufzeiten und Leistungsverluste zu reduzieren. Zwar verwendete die Methode gelegentlich mehr Vias, um Staus zu umfahren, doch dieser Kompromiss verbesserte die Flächennutzung und reduzierte die Überfüllung einzelner Lagen. In puncto Geschwindigkeit ermöglichte das One-Pass-Design zusammen mit adaptivem lokalem Scannen, dass die meisten Entwürfe in Sekunden abgeschlossen wurden; in manchen Szenarien reduzierte die adaptive Suche die Routing-Zeit gegenüber einer brutalen Vollplatten-Suche um über 90 %, bei nur geringfügig längerer Leitungslänge.

Was das für die Zukunft der Elektronik bedeutet

Vereinfacht gesagt bietet 3D LineExplore PCB-Entwicklern eine Möglichkeit, dichte Mehrlagen-Platinen ähnlich wie ein erfahrener Mensch zu routen: lokal schauen, nur die nützlichsten Kandidatenrouten auswählen und kurze Wege gegen die Kosten eines Lagenwechsels abwägen. Es vermeidet den hohen Aufwand feiner Raster, respektiert dabei strenge Designregeln und erzeugt glatte, herstellbare Leiterbahnen. Während Elektronik weiterhin komplexer wird und schrumpft, könnten Ansätze wie dieser – besonders in Kombination mit künftiger maschineller Lernunterstützung – das automatische Routing schneller und verlässlicher machen, neuen Gerätegenerationen schneller zur Marktreife verhelfen und deren Effizienz steigern.

Zitation: Sun, N., Zhang, J., Xu, N. et al. 3D LineExplore: a 3D line exploration method for multi-layer PCB geometric routing. Sci Rep 16, 6588 (2026). https://doi.org/10.1038/s41598-026-36925-0

Schlüsselwörter: PCB-Routing, Mehrlagige Leiterplatten, gitterloser Algorithmus, elektronische Design-Automation, 3D-Wegplanung