Clear Sky Science · de

Verbesserung der Gleichmäßigkeit beim HARC-Ätzen durch Kanten-Bias-Spannung und strukturelle Impedanzänderungen in einer rechteckigen Spannungswellenform

Warum Chiphersteller an geraden Löchern interessiert sind

Moderne Speicherchips pressen mehr Informationen auf kleineren Raum, indem sie Milliarden ultratiefer, bleistiftdünner Löcher in Silizium bohren. Diese „High-Aspect-Ratio“-Bohrungen müssen nahezu perfekt vertikal sein; schon leichte Neigung oder Formverzerrung können ein Bauteil unbrauchbar machen und die Produktionsausbeute drastisch senken. Diese Arbeit zeigt einen neuen Weg, um solche Löcher über die gesamte Siliziumscheibe hinweg gerade und gleichmäßig zu halten, indem man steuert, wie elektrische Felder am Scheibenrand während des Plasmaätzens wirken.

Das Problem mit dem empfindlichen Rand der Wafer

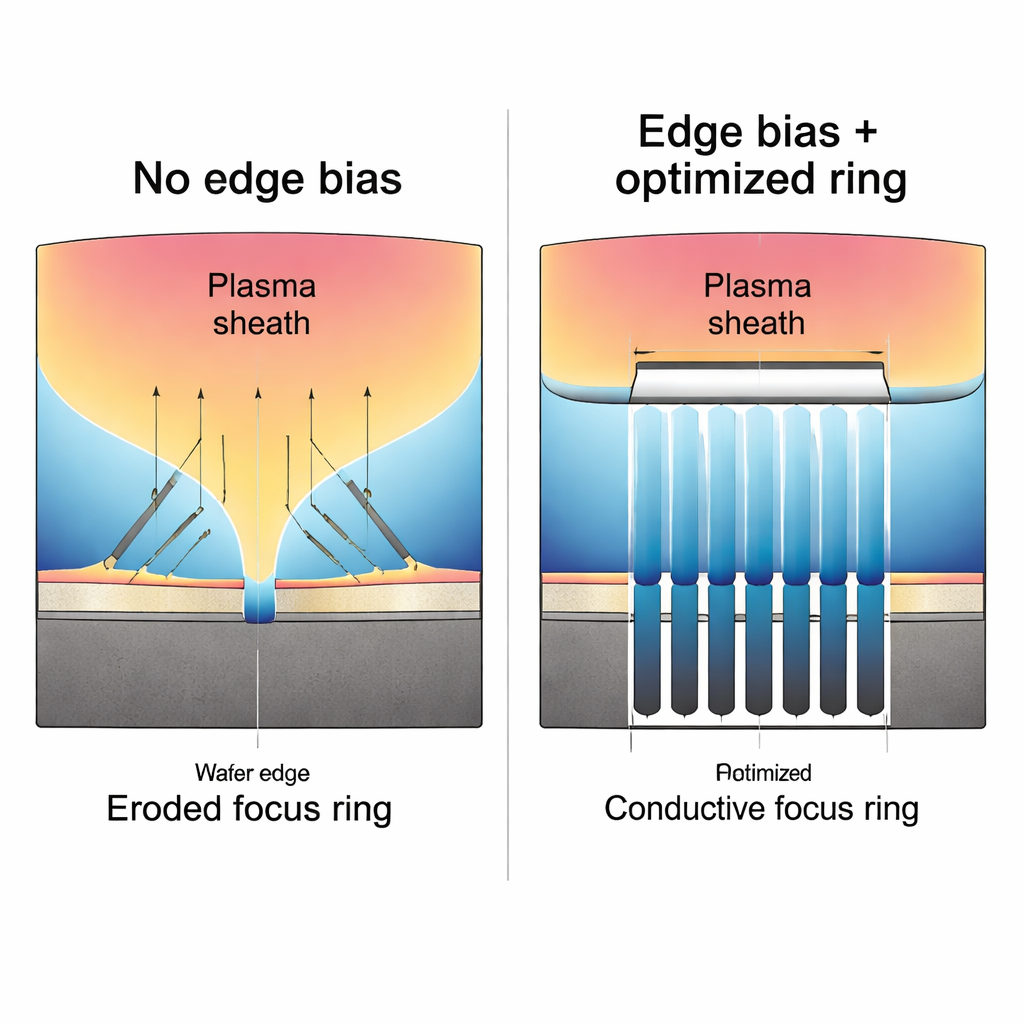

Um Muster in eine Wafer zu schneiden, setzen Hersteller Plasma ein — ein leuchtendes Gas voller energiereicher Ionen, die Material wegblasen. Um die Wafer liegt ein opfernder „Focus Ring“, der hilft, das Plasma vom Zentrum bis zum Rand gleichmäßig zu halten. Im Laufe der Zeit wird dieser Ring durch dieselbe harte Umgebung, die den Chip ätzt, abgetragen. Während er erodiert, verformt sich die elektrische Schicht (Sheath), die Ionen zur Waferoberfläche lenkt, besonders am Rand. Statt senkrecht einzuschlagen, treffen die Ionen in einem Winkel auf, wodurch Löcher zur Mitte hin kippen und sich zu Ellipsen dehnen. Das verzerrt nicht nur winzige Kondensatorstrukturen, sondern reduziert auch die nutzbare Fläche und senkt die Ausbeute.

Ein steuerbares „Lenkrad“ am Rand ergänzen

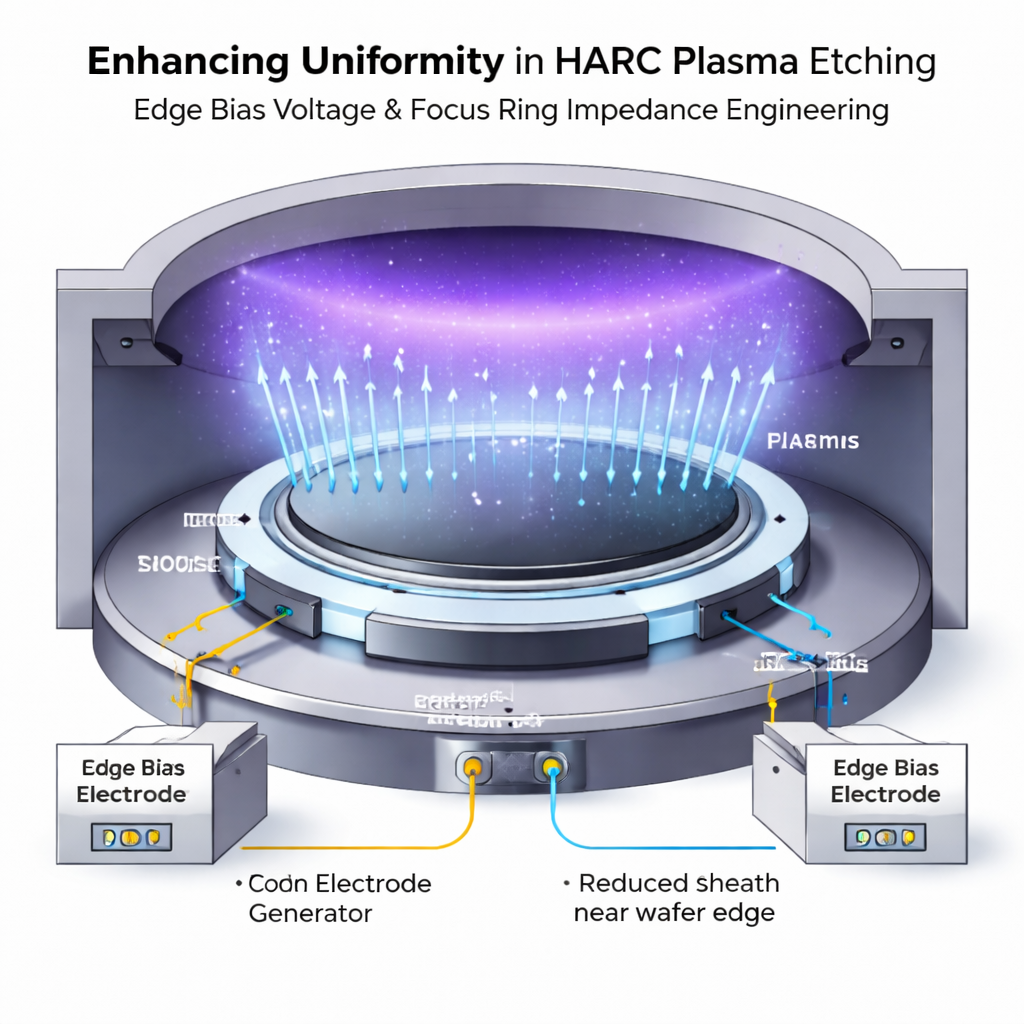

Die Forscher gingen dieses Problem an, indem sie unter dem Focus Ring eine unabhängig geregelte Kantenelektrode einbauten, die mit einer rechteckförmigen Bias-Spannung betrieben wird, getrennt von der Haupt-Bias für die Wafer. Statt der üblichen glatten Sinuswelle schaltet diese quasi-quadratische Wellenform scharf zwischen an und aus und hält den Spannungsunterschied zwischen Plasma und Oberfläche zeitlich konstanter. Dieser gleichmäßigere Schub lässt die Ionen mit engerem Energiespektrum und kleinerem Winkelbereich eintreffen. Durch gezieltes Anheben der Kanten-Bias konnten die Forscher die elektrische Sheath am Waferrand verstärken und umformen, die Ionenbahnen wieder mehr in die Vertikale ziehen und selbst dort zirkulare, gut definierte Grabenprofile zurückgewinnen, wo der Focus Ring bereits verschlissen war.

Wenn mehr Leistung alles verschlimmert

Allerdings schuf ein zu starkes Erhöhen der Kanten-Spannung ein neues Problem. Bei etwa 280–300 Volt verursachte die elektrische Wechselwirkung zwischen der Kanten- und der Zentrumselektrode unerwünschte Leckströme durch das Plasma. Messungen zeigten wachsende Diskrepanzen zwischen der vom Gerät angelegten und der tatsächlich an der Waferoberfläche auftretenden Spannung sowie steigende Ströme im Waferbereich. Das störte die sorgfältig eingestellte Sheath, machte das Plasma instabil und führte zu erneut ungleichmäßigem Ätzen: Mittlere Bereiche wurden schneller geätzt, der Rand verlangsamte sich, und die Lochformen verzerrten sich trotz höherer Kanten-Bias wieder.

Die Hardware umgestalten, um die Felder zu zähmen

Um bei hohen Spannungen die Kontrolle zurückzugewinnen, überarbeitete das Team den Aufbau der isolierenden und leitfähigen Schichten um die Wafer — insbesondere die Materialien unter und um den Focus Ring. Durch den Austausch von Bauteilen und die Änderung ihrer elektrischen Eigenschaften stellten sie das Impedanzverhältnis zwischen dem Fokus-Ring-Pfad und dem Wafer-Chuck neu ein. Ein höheres Verhältnis (etwa 1,31) begrenzte die unerwünschte Kopplung zwischen den beiden Bias-Schaltkreisen, sodass die Kanten-Bias ihre Aufgabe erfüllen konnte, ohne das Zentrum mitzuziehen. Experimente zeigten, dass mit dieser optimierten Konfiguration Gräben selbst bei 300 Volt Kanten-Bias nahezu kreisförmig und vertikal blieben und die Ätzrate über die Waferfläche viel gleichmäßiger war. Computersimulationen stützten dies und zeigten, wie verschiedene Focus-Ring-Materialien (Silizium versus Quarz) Sheath-Dicke, Plasmadichte und die Stärke des vertikalen elektrischen Felds verändern.

Was das für künftige Speicherchips bedeutet

Für Nichtfachleute ist die Kernbotschaft, dass die Autoren einen Weg gefunden haben, die unsichtbaren elektrischen Felder am Waferrand so „zu steuern“, dass Plasmaionen geradere, konstantere Löcher bohren. Durch die Kombination einer separat geregelten, rechteckigen Kanten-Bias mit einer elektrisch optimierten Trägerstruktur können sie sowohl Kantenneigung korrigieren als auch Instabilitäten vermeiden, die beim zu starken Anheben der Spannungen auftreten. Dieser Ansatz sollte Herstellern helfen, präzise, tiefe Strukturen zu ätzen, während Speicherzellen weiter schrumpfen, und so die Ausbeute und Zuverlässigkeit zukünftiger Halbleiterbauteile verbessern.

Zitation: Park, C., Cho, J., Um, J. et al. Enhancing uniformity in HARC etching via edge bias voltage and structural impedance variations in a rectangular voltage waveform. Sci Rep 16, 5851 (2026). https://doi.org/10.1038/s41598-026-36323-6

Schlüsselwörter: Plasmaätzen, Halbleiterfertigung, hohes Seitenverhältnis, Kanten-Bias-Spannung, Focus-Ring-Design