Clear Sky Science · ar

حساب فعال وتصميم بنية مضاعف فيديك مزدوج الدقة عالي السرعة

لماذا تهم زيادة سرعة حساب الأرقام

في كل مرة تشغل فيها فيديوً مباشراً، تستخدم فيها خرائط الملاحة على هاتفك، أو تطلب من نظام ذكاء اصطناعي تحليل صور طبية، تقوم وحدات معالجة متخصصة بهدوء بتنفيذ مليارات الحسابات الصغيرة في الثانية. جزء كبير من هذه العمليات هي ضربات على أعداد ذات فاصلة عائمة، وهي الطريقة القياسية التي تمثل بها الحواسيب القيم الحقيقية مثل 3.14159. تستعرض هذه الورقة طريقة أذكى لبناء أحد هذه المكونات الأساسية: مضاعف عالي السرعة وموفّر للطاقة يستوحي أفكاراً من رياضيات فيديك القديمة لتعزيز العتاد الرقمي الحديث.

من حِيَل حسابية قديمة إلى رقائق حديثة

تدعم الحسابات ذات الفاصلة العائمة معالجة الإشارات الرقمية، ومعالجة الصور، والاتصالات، ومسرِّعات التعلم العميق. يجب أن تتعامل المضاعفات القياسية مع كلمات ثنائية عريضة—64 بت للدقة المزدوجة—وبسرعة دون إهدار مساحة الشريحة أو الطاقة. تقاربات تقليدية مثل بوث وكاراتسوبا ومضاعفات المصفوفة توازن بين السرعة وحجم العتاد وتعقيد التصميم. تتضمن رياضيات فيديك، وهي نظام مكوَّن من 16 قاعدة حسابية كلاسيكية نشأت في الهند، طريقة ضرب تسمى Urdhva Tiryakbhyam أو «عمودي ومُتقاطع». تُشكّل هذه الطريقة المنتجات الجزئية بشكل متوازي للغاية، ما يمكن أن يقلّل عدد الخطوات الوسيطة والعتاد المطلوب. قام الباحثون مؤخرًا بتكييف هذه الأفكار للدارات الرقمية، لكن التصاميم الحالية ما تزال تتحمل أعباء إضافية عند استخدامها لعمليات الفاصلة العائمة مزدوجة الدقة.

ما الذي يميز هذا المضاعف الجديد

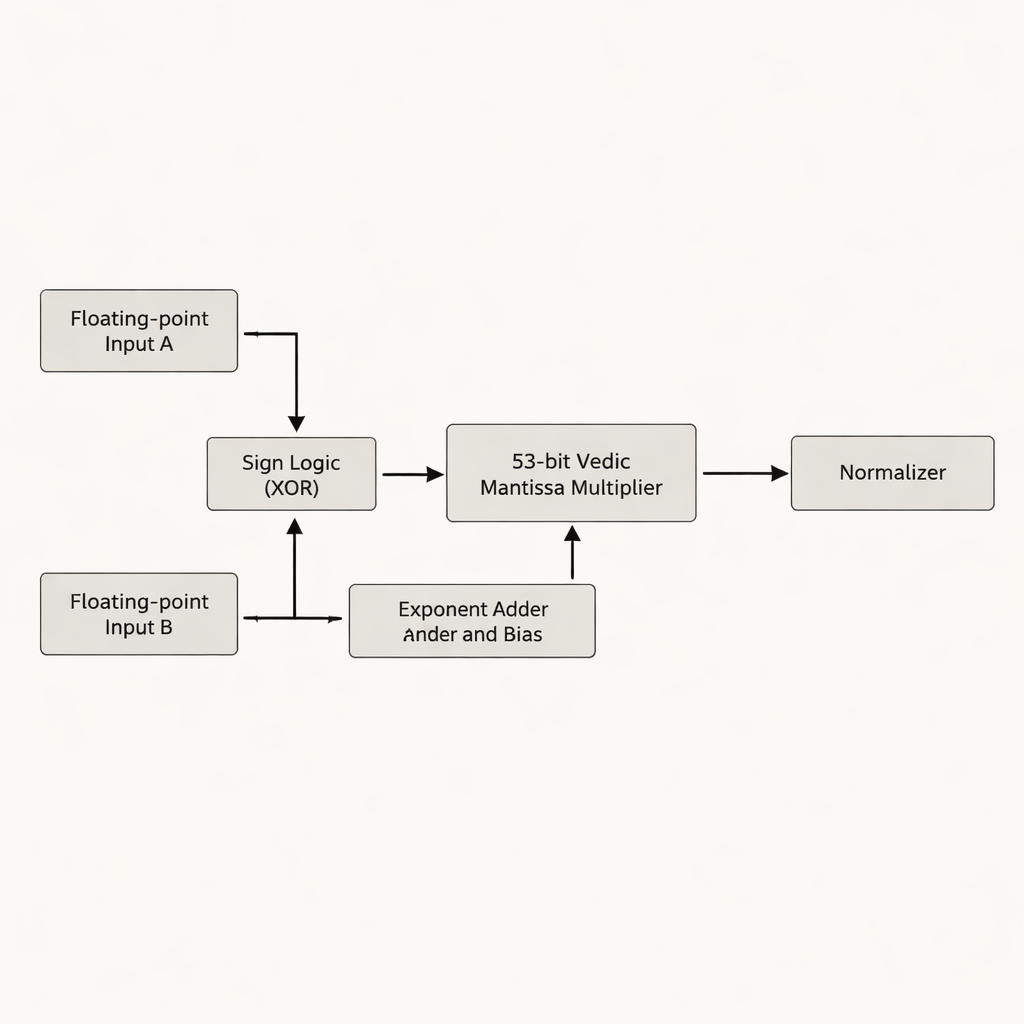

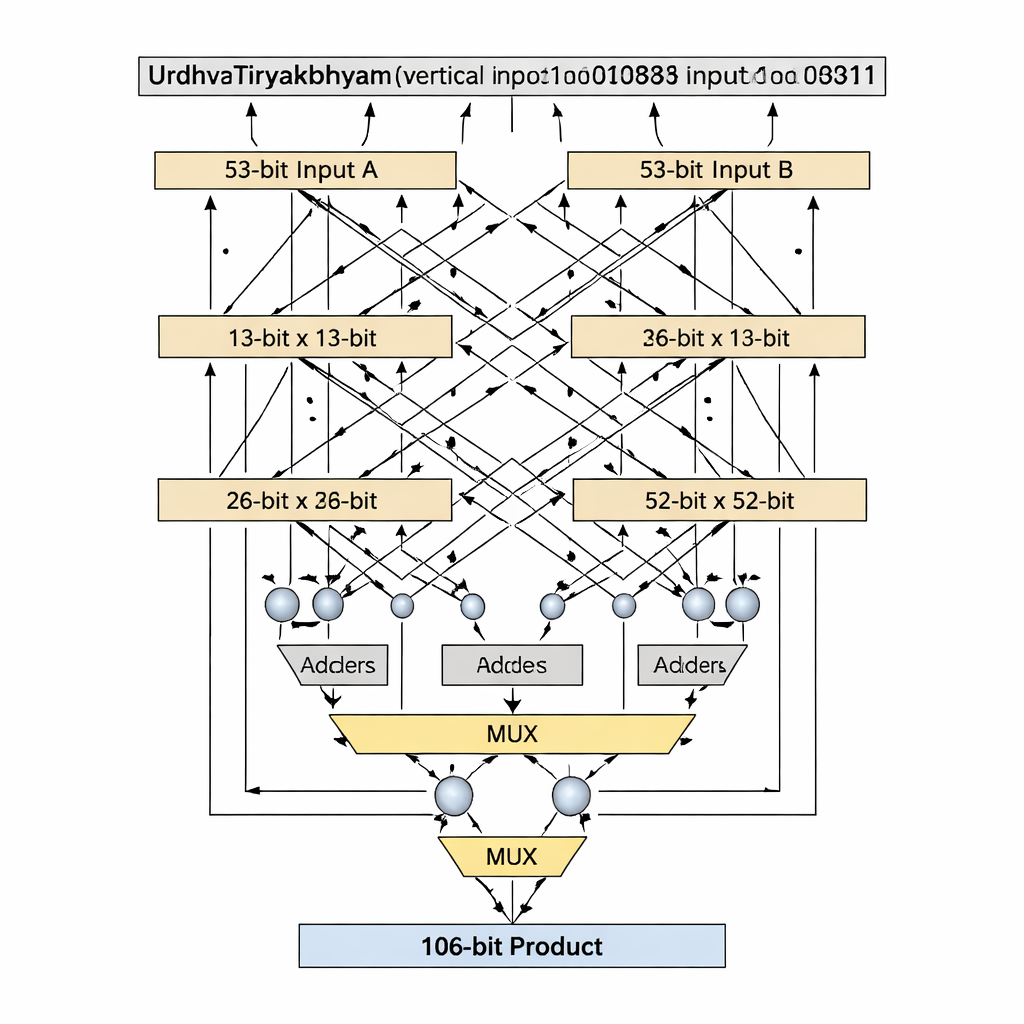

يقترح المؤلفون مضاعف فاصلة عائمة مزدوج الدقة يركّز على المانتيسا—الجزء من الرقم العائم الذي يحتوي معظم الأرقام المهمة. بدلاً من حشو المانتيسا ذات 52 بت إلى 54 بت كما تفعل العديد من التصاميم السابقة، يعملون مع المانتيسا الفعلية ذات 53 بت الفعّالة، متجنبين بتات «مساحة بيضاء» مهدرة تستهلك تخزينًا وأسلاكًا إضافية على الشريحة. جوهر التصميم هو مضاعف فيديك بطول 53 بت مبني على Urdhva Tiryakbhyam، مرتب في هيكلية من كتل أصغر: وحدات 3 بت تشكّل وحدات 6 بت، التي تبني وحدات 12 بت، 13 بت، 26 بت، و52 بت، جميعها مدمجة في مرحلة نهائية بطول 53 بت. تفصل البنية العمل إلى ثلاث مراحل رئيسية—حساب الإشارة، جمع الأسّ والمواءمة، وضرب المانتيسا تليه المعايرة—مطابقة لمعيار IEEE-754 للفاصلة العائمة مع تقليص الدوائر الزائدة.

كتل بناء ذات أطوال أولية لعتاد أنظف

ابتكار رئيسي هو كيفية تعامل التصميم مع أطوال البتات التي هي أعداد أولية، مثل 13 و53، والتي لا تقسم بسهولة إلى كتل متساوية. تفترض تفكيكات فيديك القياسية مدخلات مقسمة بالتساوي، لكن ذلك يصبح محرجًا أو مهدراً للأجزاء الأولية للأطوال الأولية. يقدم المؤلفون خوارزمية «البت الأولي» التي تعيد بذكاء استخدام مضاعف فيديك أصغر بحجم (n−1) بت، بالإضافة إلى جامعات، ومبدلات اختيار، وبوابة منطقية إضافية واحدة، لمحاكاة مضاعف n بت دون حشوة. لمرحلة 13 بت، تُقسَم المدخلات إلى قسم بطول 1 بت وآخر بطول 12 بت؛ تُنشأ المنتجات الجزئية باستخدام مضاعف فيديك 12 بت، والاختيار الشرطي (عبر المبدلات) بناءً على البتات الأهم، وعدد قليل من الجامعات. يتوسع نفس النمط إلى 53 بت مع نواة 52 بت. يقصر هذا التفكيك المصمم المسار الحرج—أطول سلسلة من المنطق يجب أن يقطعها الإشارة—مع الحفاظ على عدد منخفض من عناصر المنطق.

مكاسب مقاسة في السرعة والحجم والطاقة

وُصِف التصميم بلغة وصف الأجهزة Verilog ونُفّذ على مصفوفة بوابة قابلة للبرمجة ميدانياً من طراز Xilinx Zynq باستخدام أدوات Vivado. عبر مضاعفات فيديك بطول 13 و26 و52 و53 و64 بت، تُظهر الوحدة المقترحة بطول 53 بت توازناً ممتازاً بين التأخير، واستخدام المنطق (جداول البحث ومنافذ الإدخال/الإخراج)، والطاقة المقدرة. مقارنةً بمضاعفات مزدوجة الدقة السابقة المبنية على بوث وكاراتسوبا وترتيبات فيديك أخرى، تقلّل البنية الجديدة بشكل كبير من أقصى تأخير ومن كمية موارد الـ FPGA المطلوبة، دون زيادة تعقيد الدوائر المحيطة بالفاصلة العائمة. وبما أن ضرب المانتيسا أسرع وعمق المنطق أضيق، ينخفض نشاط التحويل، ما يشير إلى منتج طاقة–تأخير أفضل رغم صعوبة إجراء مقارنات طاقة مباشرة عبر تقنيات مختلفة.

تأثيرات على الذكاء الاصطناعي ومعالجة الإشارات

لاختبار التصميم في عبء عمل حقيقي، دمج المؤلفون مضاعفهم الفيديكي مزدوج الدقة في محرك الالتفاف لشبكة عصبية التفافية، حيث تهيمن عمليات الضرب والجمع التراكمي على وقت التشغيل. أدى استبدال المضاعفات التقليدية وفق معيار IEEE-754 والمضاعفات الفيديكية السابقة بالتصميم الجديد إلى تقليص زمن الالتفاف، وخفض استهلاك الطاقة، وتقليل زمن الاستدلال، كل ذلك مع الحفاظ على نفس دقة التصنيف. من المتوقع أن تظهر فوائد مماثلة في مهام حوسبية مكثفة أخرى، مثل التصفية الرقمية، واكتشاف الحواف، وسلاسل أنابيب التصوير الطبي، حيث تزيد المضاعفات الأسرع معدل المعالجة مباشرة ويمكن أن تسمح للأجهزة بالتشغيل بدرجات حرارة أقل أو على بطاريات أصغر.

ما الذي يعنيه هذا لتقنية الحياة اليومية

بعبارات بسيطة، تُظهر الورقة أن استعارة فكرة ضرب ذكية من رياضيات فيديك ومطابقتها بعناية مع صيغ ثنائية حديثة يمكن أن تنتج مضاعفًا أصغر وأسرع وأكثر كفاءة في الطاقة من التصاميم القياسية. يمكن إدراج هذا المبنى المحسّن في المعالجات، وشرائح معالجة الإشارات، ومسرِّعات الذكاء الاصطناعي، مما يؤدي إلى تحليل بيانات أسرع، وأجهزة أكثر استجابة، وربما انخفاض استهلاك الطاقة في أنظمة تتراوح من الهواتف الذكية إلى الماسحات الطبية. كما يحدد المؤلفون اتجاهات مستقبلية، بما في ذلك المنطق القابل للعكس لاستهلاك طاقة أقل ودمجًا في وحدات معالجة أكبر، ما يشير إلى أن هذا الزواج بين الحساب القديم والعتاد الحديث ما زال في بداياته.

الاستشهاد: Kumar, A.S., Sahitya, G., Kusuma, R. et al. Efficient computation and design of high speed double precision Vedic multiplier architecture. Sci Rep 16, 7364 (2026). https://doi.org/10.1038/s41598-026-38147-w

الكلمات المفتاحية: مضاعف فيديك, الحساب ذو الفاصلة العائمة, تصميم FPGA, معالجة الإشارات الرقمية, الشبكات العصبية الالتفافية